Synopsys – Latency Prediction for On-chip Communication #SWI2019

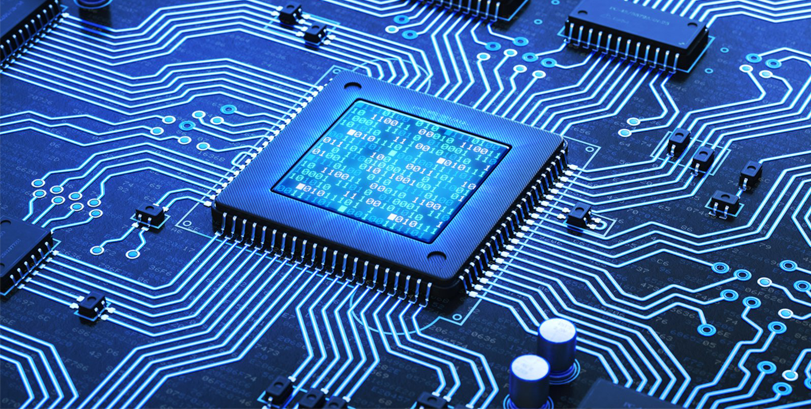

When placing components on a chip one is faced with several objectives. A major objective is that the length of the connections between the components should be minimal. For this aspect heuristic algorithms are available.

Another objective is that the envisioned clock frequency can be met, or at least have the smallest violation. This frequency is determined by the delay (or latency) of signals that travel between components.

The latency of a signal is determined by the electrical resistances and capacitances of the connections and components. The complexity of the problem arises from the fact that these electrical properties may depend on decisions that are made later in the design flow. E.g. different metal layers on the chip give rise to different electrical properties but allocating connections to the metal layers is done after placement.

Another complicating factor is that one may insert repeaters on the connections to boost/speedup the signal. However, these repeaters introduce extra latency. These repeaters are especially needed when the connections are long or when connections do not point to point. Developing an algorithm that estimates the latency of on-chip connections is our challenge for SWI 2019.

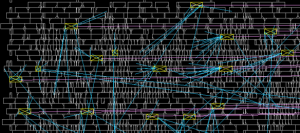

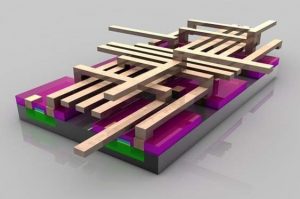

Top Left: logical connections between some components as seen during component placement

Bottom Left: Connections with assigned metal layers (different colors) as determined after component placement

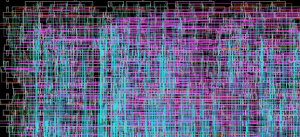

Bottom Right: 3D-illustration of connections in different layers